Faculty of Computer Science

Center for Advancing Electronics Dresden Chair for Compiler Construction

### **Master Thesis**

# Compiler-Assisted Speculative Decoding for Accelerated LLM Inference on Heterogeneous Edge Devices

Alejandro Ruiz y Mesa

Matriculation number: 5126441

to achieve the academic degree

Master of Science (M.Sc.)

First referee

Prof. Dr.-Ing. Jerónimo Castrillón

Second referee

Dr.-Ing. Asif Ali Khan

Supervisors

Dr. João Paulo Cardoso de Lima

Dr. Guilherme Korol

M.Sc. Moritz Riesteter

Submitted on: 31st October 2025

TU Dresden Fakultät Informatik, Institut für Technische Informatik, Professur für Compilerbau

### Task Description for Master Thesis

For: Alejandro Ruiz y Mesa

Degree program: Nanoelectronic Systems (Master)

Matriculation number:

E-mail: alejandro.ruiz\_y\_mesa@mailbox.tu-dresden.de

Topic: Compiler-Assisted Speculative Decoding for Accelerated LLM

Inference on Heterogeneous Edge Devices

Large Language Models (LLMs) are the state-of-the-art of many Artificial Intelligence (AI) tasks. However, the size (billions of parameters) and complexity (hundreds of layers) of these models difficult their wider adoption at the Edge - where resources are restricted. On one hand, modern hardware heterogeneity can help deploying efficient LLM inference on edge devices. With multiple types of processing units, such as CPUs, GPUs, and NPUs, one can optimize the heavy-load LLMs for performance at controllable levels of energy consumption. Still, running LLMs at the edge challenges users given the lack of mature end-to-end AI compilation flows. Compilers like IREE, built upon the MLIR infrastructure, enable users with a flexible front-end and a modular compilation flow supporting heterogeneous hardware targets. However, even this MLIR-based mechanism currently relies on manual intervention and lacks a deeper understanding of the LLM models that can drive further performance improvements.

On the other hand, LLMs optimizations have been proposed to lower the LLMs cost. Particularly, Speculative decoding (SD) is a generation-refinement technique that addresses the sequential bottleneck of the autoregressive generative models. SD reduces latency by anticipating likely outcomes in the model's prediction sequence. Nonetheless, its efficiency critically depends on how the inherent algorithmic bottlenecks are managed and whether the speculative execution phase can effectively leverage the capabilities of heterogeneous hardware. Addressing these concerns is essential for enhancing overall inference performance, particularly in resource-constrained edge devices.

The project task focuses on addressing these challenges by integrating speculative decoding awareness into the MLIR-based IREE compiler. The first step is to systematically identify and analyze the bottlenecks within speculative decoding algorithm implementations. This profiling will enable us to assess where delays in the speculative phase occur and whether these may be mitigated through the use of the available heterogeneous processing units. To achieve this, the student will design and implement an annotation system within the IREE compilation flow to partition the model's graph between the SD components. With the partioning at hand, compile-time layer-wise decisions will be made to dispatch the bottleneck components to the most suitable processing unit.

For evaluating this proposal, the student will use a board containing heterogeneous ARM's Cortex cores and Mali GPU. The proposal will be assessed against CPU- and GPU-only executions of IREE-compiled SD models.

Start: 01.05.2025 31.10.2025End:

1<sup>st</sup> referee: Prof. Dr.-Ing. Jerónimo Castrillón

2<sup>nd</sup> referee: Dr.-Ing. Asif Ali Khan

Supervisor: Dr. João Paulo Cardoso de Lima

Dr. Guilherme Korol Co-supervisor:

Jeronimo Castrillon Mazo Date: 2025.04.14 07:27:53

Digitally signed by Jeronimo Castrillon Mazo

Prof. Dr.-Ing. Jerónimo Castrillón (Professor in charge)

# Statement of authorship

I hereby certify that I have authored this document entitled Compiler-Assisted Speculative Decoding for Accelerated LLM Inference on Heterogeneous Edge Devices independently and without undue assistance from third parties. No other than the resources and references indicated in this document have been used. I have marked both literal and accordingly adopted quotations as such. There were no additional persons involved in the intellectual preparation of the present document. I am aware that violations of this declaration may lead to subsequent withdrawal of the academic degree.

Dresden, 31st October 2025

Alejandro Ruiz y Mesa

Faculty of Computer Science Chair for Compiler Construction

### **Abstract**

The growing demand for on-edge computing has intensified the need to reduce inference latency on resource-constrained devices. These systems increasingly rely on heterogeneous hardware, such as CPUs, GPUs, and NPUs, to efficiently execute diverse workloads. Large Language Models (LLMs) are at the core of many edge applications, including health assistants, translation, and interactive dialogue systems. However, their autoregressive decoding process introduces a sequential bottleneck that limits parallelization. Speculative decoding has emerged as a promising approach to mitigate this limitation by generating multiple tokens in parallel while maintaining model performance.

This work addresses two interrelated problems. The first concerns performance and productivity: integrating an autoregressive generative pipeline with speculative decoding into a compilation flow, without sacrificing runtime efficiency, while preserving modularity, composability, and ease of use. The second problem raises from the compute diversity present in edge devices and focuses on heterogeneous partitioning: optimal assignment of subgraphs from an LLM with speculative decoding across different processing units (PUs) within a system-on-chip (SoC), particularly during the prefill phase and for short input sequences (which is characteristic of edge workloads). To solve these challenges, we propose an analytic cost model that explores multiple heterogeneous hardware configurations and supports coarse-grained partitioning strategies.

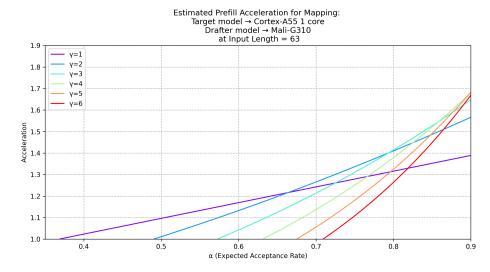

The analytic exploration reveals a maximum speedup of  $1.68\times$  for a translation task with a 90% acceptance rate when combining speculative decoding with heterogeneous execution. Moreover, for lower acceptance rates or heterogeneous system settings, speculative decoding incurs excessive overhead and heterogeneous execution offers no benefit. The proposed analytic cost model was validated on a edge device confirms the model's predictive accuracy, showing the speedup of  $1.68\times$  is achieved at an acceptance rate four percentage points higher than expected. While focused on the prefill phase and short sequences, the proposed framework generalizes to other hardware configurations, inference phases, and speculative decoding techniques.

# **Contents**

| ΑI | ostrac | VI                                                                  | ı  |

|----|--------|---------------------------------------------------------------------|----|

| Sy | mbol   | and Acronyms                                                        | Ĭ. |

| 1  | Intr   | duction                                                             | 1  |

|    | 1.1    | Goal                                                                | 2  |

|    | 1.2    | Structure of the Work                                               | 3  |

| 2  | Bac    | ground                                                              | 5  |

|    | 2.1    | Edge Processing and Heterogenous Compute                            | 5  |

|    |        | 2.1.1 Edge Processing                                               | 5  |

|    |        | 2.1.2 SoCs as Heterogeneous Edge Devices                            | 6  |

|    | 2.2    | Large Language Model Inference                                      | 7  |

|    |        | 2.2.1 Transformer Architecture                                      | 7  |

|    |        | 2.2.2 Autoregressive Generation                                     | 8  |

|    |        | 2.2.3 Inference Regimes                                             | 8  |

|    | 2.3    | Speculative Decoding as a Token Generation Optimization Technique   | 9  |

|    |        | 2.3.1 Speculative Decoding Overview                                 | 0  |

|    |        | 2.3.2 Dependence on Hardware and Software Configurations            | 1  |

|    | 2.4    | Machine Learning Compilers                                          | 2  |

|    |        | 2.4.1 Domain-Specific Compilers                                     | 2  |

|    |        | 2.4.2 Multi-Level Intermediate Representation Approach for Compiler |    |

|    |        | Construction                                                        | 3  |

|    |        | 2.4.3 IREE as a Compiler for Machine Learning                       | 3  |

|    |        | 2.4.4 Runtime for Heterogeneous Devices                             | 5  |

| 3  | Rela   | ed Work                                                             | 7  |

|    | 3.1    | Neural Network Optimization Methods                                 | 7  |

|    | 3.2    | Parallelism on Heterogenous Hardware                                | 8  |

|    | 3.3    | Machine Learning Compilers                                          | 8  |

|    | 3.4    | Thesis Contributions                                                | q  |

| 4 | Met | thods a | nd Implementation                                                   | 21 |

|---|-----|---------|---------------------------------------------------------------------|----|

|   | 4.1 | Expres  | ssing Speculative Decoding Pipelines Ahead of Time                  | 21 |

|   |     | 4.1.1   | Matching Abstractions of Speculative Decoding and Heterogenous      |    |

|   |     |         | Execution                                                           | 21 |

|   |     | 4.1.2   | Implementation of a Monolithic Graph for Edge Deployment            | 23 |

|   | 4.2 | Distrib | outing Large Language Models across Unbalanced Processing Units     | 25 |

|   |     | 4.2.1   | Evaluation Hardware                                                 | 25 |

|   |     | 4.2.2   | Assumptions                                                         | 26 |

|   |     | 4.2.3   | Design Space Encoding                                               | 27 |

|   |     | 4.2.4   | Search Method                                                       | 28 |

|   |     | 4.2.5   | Evaluation Method                                                   | 28 |

|   |     | 4.2.6   | Methodology                                                         | 29 |

| 5 | Eva | luation | and Analysis                                                        | 33 |

|   | 5.1 | Homog   | geneous Mapping and Execution                                       | 33 |

|   |     | 5.1.1   | Quantization Effects on $oldsymbol{lpha}$                           | 33 |

|   |     | 5.1.2   | Considerations for the Acceptance Rate $\alpha$ on Edge             | 34 |

|   | 5.2 | Hetero  | ogenous Mapping and Execution                                       | 34 |

|   |     | 5.2.1   | Data Collection for Modeling the Impact of Speculative Decoding and |    |

|   |     |         | Heterogenous Execution                                              | 35 |

|   |     | 5.2.2   | Estimating the Impact of Speculative Decoding and Heterogenous      |    |

|   |     |         | Execution                                                           | 37 |

|   | 5.3 | Model   | Validation                                                          | 40 |

|   |     | 5.3.1   | Methodology Changes                                                 | 40 |

|   |     | 5.3.2   | Results                                                             | 41 |

| 6 | Con | clusion | and Future Work                                                     | 43 |

| Α | Арр | endix - | Modifications to IREE Compiler (v3.6.0.)                            | 57 |

| В | Арр | endix - | Tall and Skinny Matrix Multiplication                               | 61 |

# **Symbols and Acronyms**

| $\mathbf{SoC}$ | System on Chip                         | $\mathbf{TTFT}$ | Time to First Token                           |

|----------------|----------------------------------------|-----------------|-----------------------------------------------|

| NPU            | Neural Processing Unit                 | FNN             | Feedforward Neural Network                    |

| $\mathbf{PU}$  | Processing Unit                        | MAC             | Multiply-Accumulate                           |

| SIMT           | Single Instruction Multiple<br>Threads | MLIR            | Multi-Level Intermediate<br>Representation    |

| DSAs           | Domain-Specific Architectures          | IREE            | Intermediate Representation                   |

| DSL            | Domain-Specific Language               | ID              | Execution Environment                         |

| ML             | Machine Learning                       | IR<br>SPIR-V    | Intermediate Representation Standard Portable |

| DNN            | Deep Neural Network                    | SPIR-V          | Intermediate Representation V                 |

| $\mathbf{LLM}$ | Large Language Model                   | CFG             | Control Flow Graph                            |

| CNN            | Convolutional Neural Network           | AOT             | Ahead-of-Time                                 |

| KV             | Key-Value                              | $\mathbf{JIT}$  | Just-in-Time                                  |

## 1 Introduction

The development of software for edge systems has traditionally been considered challenging. This perception is rooted in the constraints inherent to edge platforms, including the limited computational budget, diverse toolchains, and vendor-specific environments. Nevertheless, the recent acceleration in hardware innovation driven by the increasing demand of edge Machine Learning (ML) has exacerbated this challenge rather than alleviated it.

The slowdown of Moore's law has marked a turning point in computer architecture, generating a proliferation of specialized hardware and heterogeneous systems; the industry has turned into architectural diversity with the development of Domain-Specific Architectures (DSAs) as the new paradigm to populate modern edge System on Chip (SoC) designs. While these developments promise significant computational advantages, they also introduce additional layers of complexity into the software stack. Compiler infrastructures and programming models often struggle to keep pace with this hardware evolution, hindering the adoption and the effective utilization of these new architectures.

For edge ML researchers and engineers, this transformation presents both opportunity and difficulty. On one hand, the availability of heterogeneous and accelerated compute enables applications once confined to data centers to run directly on the edge. On the other hand, handling this diversity of hardware requires increasingly new programming tools, making edge system design and optimization more demanding. This growing gap between the changing hardware capabilities and the software abstractions threatens to diminish the practical benefits of such advancements.

Alongside this transition to the edge, optimization techniques originally developed to mitigate computational and memory demands in cloud environments are also being adapted for edge platforms. These techniques, such as quantization or pruning, to name a few, are not only applicable but become even more critical in edge settings due to their inherent resource constraints. Transformer-based Large Language Model (LLM) architectures are an example of this: they are propagating from cloud to edge. However, the sequential nature of LLM inference, generating one token at a time, challenges hardware designed for parallelism. To address this, new acceleration strategies, such as speculative and parallel decoding, have emerged [1], [2], [3].

Speculative decoding, in particular, has demonstrated remarkable improvements in the generative pipeline on high-end GPUs, achieving speedups up to  $3\times$  or even  $6.5\times$  compared to traditional autoregressive decoding, depending on the specific technique employed [4], [5]. These results make speculative decoding an appealing candidate for migration from cloud environments to edge platforms, where computational resources are far more constrained. Despite the limited processing power of edge devices, this algorithmic optimization offers a substantial performance boost with minimal hardware overhead, requiring only a slight increase in transistor count.

However, this transition remains challenging. Current machine learning frameworks supporting speculative decoding are largely optimized for high-end hardware, reducing productivity for edge ML researchers and engineers. The dramatic speedups observed in server-class environments often fail to materialize at the edge due to the complex interplay between speculative decoding and other optimizations such as quantization. Furthermore, the inherent heterogeneity of edge devices introduces significant programmability challenges, contrasting with the homogeneous GPU-centric architectures of the cloud, where CPUs primarily handle control and synchronization tasks. In this work, we achieve a performant integration between heterogeneity, quantization, speculative decoding, on edge devices through a layered ML compiler, that allows the edge ML practitioner to exploit the available resources through ahead-of-time optimizations, overcoming the challenging scarceness of bandwidth, compute, and memory that characterizes edge systems.

### 1.1 Goal

The objective of this thesis is to demonstrate that the complexity introduced by hardware heterogeneity during the application of speculative decoding to quantized LLMs running on edge devices can be effectively leveraged through an appropriate compiler design. By employing a layered and modular compiler architecture, it is possible to abstract low-level hardware details, thereby reducing programming complexity while maintaining or improving performance. Concretely, this work aims to illustrate how an open-source ML compiler and its frontend can be used to abstract and lift low-level hardware features to enable efficient acceleration of LLM inference using speculative decoding. This research is guided by two central questions:

- 1. Is it beneficial to lift hardware abstractions and adopt a monolithic representation of the generative pipeline? This question examines whether deploying generative models in edge environments can be simplified without sacrificing performance. Specifically, it explores two strategies: 1) exposing low-level hardware features, such as heterogeneity, to the frontend, and 2) representing the entire generative pipeline in a unified graph to minimize dependencies and to facilitate global optimizations.

- 2. Under what conditions do heterogeneous execution and speculative decoding yield performance improvements on edge devices? Here, we aim to examine the effect of applying heterogeneous execution to complement speculative decoding. Given the wide variability in edge hardware configurations, the application of these two ML optimization techniques (speculative decoding and ML hardware acceleration) is non-trivial. To inform design decisions and ensure a close-to-optimal performance, we

propose the use of an analytical cost model that determines the conditions under which these techniques should be applied.

### 1.2 Structure of the Work

This thesis begins by explaining the fundamental concepts that form the basis for the work, including heterogeneous edge computing and speculative decoding in LLM inference. We also introduce ML compilers as a means to bridge the gap between fast-paced algorithmic innovation and evolving computer architectures; these foundational topics are covered in Chapter 2. In Chapter 3, we review relevant literature to contextualize our approach. Chapter 4 details the methodology used to address the core research questions, including our evaluation strategy. In Chapter 5, we present and analyze the results of our empirical study, discussing latency differences and their implications. Finally, Chapter 6 concludes our journey by summarizing our contributions, reflects on limitations, and outlines potential directions for future research.

# 2 Background

In this chapter we introduce the technical background that supports the work of this thesis. First, we present the key drivers of heterogenous edge processing. It briefly compares the cloud and edge computing emphasizing their complementarity and their trade-offs. Afterwards, we shift the focus to edge devices, bringing up a particular SoC as a paradigmatic representative of heterogenous edge devices; it comprises a CPU, GPU, among other units. The chapter then introduces the speculative decoding technique, which is a key algorithm-level optimization. Afterwards, we highlight the influence that the edge hardware has on allowing an effective speculative decoding and we present key metrics supporting this. Finally, the chapter presents ML compilers and runtimes as main building blocks that connect the inference of LLMs with the hardware heterogeneity that dominates the computation on edge-grade devices.

### 2.1 Edge Processing and Heterogenous Compute

The convergence of edge devices and LLMs has generated renewed interest in the trade-offs between cloud and on-device inference. Pushing some Deep Neural Network (DNN) workloads that have been traditionally run in the cloud to edge devices can reduce user latency and offload recurring network and cloud costs to end devices, but at the expense of dealing with constrained device resources and increased system complexity [6]. This has been possible thanks to advances in edge hardware and integration of heterogenous Processing Unit (PU)s on a single silicon die.

### 2.1.1 Edge Processing

The demand for edge compute is expanding rapidly and the market is reacting, mainly driven by the increasing need for real-time responsiveness, data privacy, and operational efficiency [7]. Tasks traditionally executed in centralized cloud infrastructures are progressively migrating toward the edge, where computation occurs closer to the data source. This shift is motivated by several factors: stringent privacy requirements, the need to reduce operational and transmission costs, the limitations of network bandwidth, and the latency constraints inherent to cloud-based processing. Among the computational workloads undergoing this transition, the deployment of transformer-based LLM architectures exemplifies this trend.

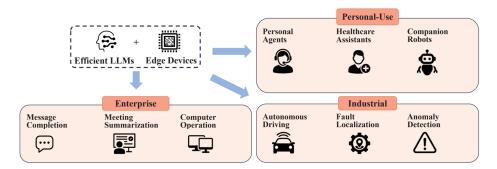

Beyond the migration of existing workloads, entirely new applications are emerging at the edge, enabled by advances in model compression, quantization, and hardware-software co-design. These include privacy-preserving inference, autonomous control, and real-time responsiveness. Figure 2.1 illustrates a selection of application domains for edge devices. For instance, personal agents such as AutoDroid [8] leverage edge-deployed LLMs to automate daily routines on the phone. In healthcare, model collections like BioMistral [9] facilitate real-time diagnostics and multimodal analysis directly on-device, enhancing confidentiality. Industrial applications, including AnomalyGPT [10] for fault detection, demonstrate the viability of deploying LLMs in latency-critical environments.

Figure 2.1: Some applications of on-device applications of LLMs. Adapted from [11].

### 2.1.2 SoCs as Heterogeneous Edge Devices

Edge devices are fundamentally resource-limited, an issue that exacerbates with more data and compute intensive workloads, such as LLMs. Performing LLM inference on edge evidences the limitations of this type of hardware, as it is largely memory-bound, which means that memory bandwidth and capacity often dominate the performance bottlenecks [12]. Additionally, continuous execution of LLMs remains elusive on edge devices, particularly on battery-powered ones [13], where thermal dissipation and battery draining issues become difficult to avoid.

The answer to this power challenge is the integration of DSAs in a single chip leading to heterogeneity in compute. This approach not only decreases the energy consumption by integrating specialized architectures for the efficient execution of a specific pattern (i.e., heavy computational operations in transformer architectures), it also increases programming complexity, since aspects such as data movement, scheduling, memory tiling, and synchronization across compute elements become essential [11].

The Google Tensor G Series [14], AMD Versal AI Edge Series [15], Rockchip RK3588 [16], NVIDIA Jetson Nano [17], STMicroelectronics STM32MP157 [18], and NXP i.MX95 [19], among others, exemplify the architectural heterogeneity that characterizes modern edge devices. These SoC platforms integrate diverse PUs including CPUs, GPUs, and increasingly Neural Processing Unit (NPU)s within a single package, designed to balance energy efficiency with computational performance. The CPUs provide general-purpose flexibility, however their sequential execution model limits their effectiveness for parallel workloads typical of transformer-based LLMs. To address this limitation, there is a growing trend toward augmenting CPUs with vector processing units and SIMD extensions

In contrast, GPUs offer high parallelism. However, compared to server GPUs, edge GPUs have more constrained caches, shared memory, and memory bandwidth. To achieve a high

performance, shader programs must be optimized and memory layouts (e.g., PHWC4) adopted to match GPU architecture, to improve cache locality and reduce bandwidth bottlenecks [20]. Moreover, optimizations such as operator fusion, reduced kernel invocations, tiling, efficient buffer reuse, and bandwidth-aware scheduling are essential since mobile GPU's compute units are usually underutilized by the inefficient software layering [21]

### 2.2 Large Language Model Inference

Transformer-based LLMs have revolutionized natural language processing by enabling high-quality generative capabilities across a wide range of tasks. Unlike traditional architectures used in computer vision, LLMs rely on attention mechanisms and autoregressive decoding, which introduce unique challenges for inference. In this section, we provide a brief overview of the inference process in transformer-based LLMs.

### 2.2.1 Transformer Architecture

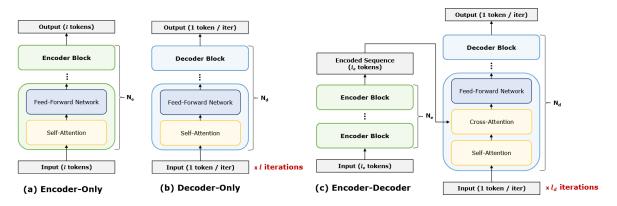

Transformers are DNN architectures built around multi-head attention mechanism, which allows models to dynamically focus on different parts of an input sequence by computing attention scores followed by softmax normalization. Each transformer block also includes feed-forward networks, residual connections, and layer normalization [22]. This is illustrated in Figure 2.2, where transformer blocks are shown in green (a) and (c), and in blue (b) and (c).

Figure 2.2: Three variants of the Transformer architecture: (a) encoder-only, (b) decoder-only, and (c) encoder-decoder. Taken from [23]

Transformers are categorized as shown in Figure 2.2. Encoder-only models (a) are used for parallel processing of input sequences in understanding task; decoder-only (b), models for sequential token generation (i.e., autoregressive generation). The encoder-decoder architecture (c) is a combination of the two previous classes. Encoder blocks scale linearly or quadratically with sequence length, while decoder blocks require iterative inference, resulting in lower arithmetic intensity and higher latency. These distinctions are discussed in more detail through this section.

### 2.2.2 Autoregressive Generation

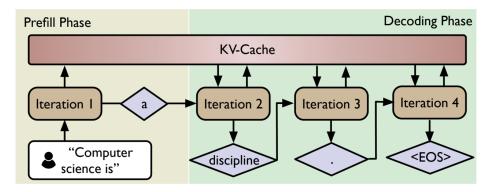

Inference in LLMs is fundamentally different from discriminative tasks, particularly due to the sequential nature of token generation in decoder-only transformer architectures: they generate one token at a time, with each step conditioned on previously generated tokens. The inference workflow is depicted in Figure 2.3; it consists of two phases:

- **Prefill Phase**: The model processes the entire input prompt to initialize the Key-Value (KV) cache.

- **Decode Phase**: The model generates one token at a time, using the previously generated token (not the entire sequence) and the KV cache.

Figure 2.3: Prefill and decode phases during LLM inference. Taken from [24]

This sequential generation leads to a shape-changing workload: the input sequence length increases with each generated token. Consequently, the memory and compute requirements vary during inference, making LLM inference more complex than traditional discriminative inference [12].

### 2.2.3 Inference Regimes

To analyze and optimize LLM inference, it is useful to distinguish between different inference regimes based on two axes: the phase of inference (prefill vs. decode) and the input sequence length  $(S_L)$  (short vs long). These regimes exhibit distinct compute and memory characteristics [25]. Although this work focuses on the prefill phase under very short input sequence regimes, we briefly introduce the remaining execution phases below for the sake of completeness.

Compute-Boundness vs Memory-Boundness Compute-bound operations are constrained by the hardware's peak floating-point throughput and benefit primarily from algorithmic optimizations that reduce arithmetic intensity. In contrast, memory-bound operations are limited by available memory bandwidth and are better accelerated through techniques such as quantization and operator fusion. The roofline model provides a framework to classify operations into these categories by comparing their arithmetic intensity (measured in FLOPs per byte) against the target hardware's ridge point, thereby guiding optimization strategies [26].

**Prefill vs Decode Phases** During the prefill phase, computation is dominated by matrix-matrix multiplications, which exhibit high arithmetic intensity and benefit from batching and parallelism. In contrast, the decode phase primarily involves matrix-vector multiplications with lower arithmetic intensity, making it more susceptible to memory bottlenecks. This phase also requires frequent access to and updates of the KV cache, further emphasizing its memory-bound nature [25].

Short vs Long Sequence Lengths In transformer-based models, the dimensionality of the hidden states, denoted as d, plays a central role in determining computational characteristics. Sequence lengths  $(S_L)$  are typically categorized relative to this dimension: short sequences are those where  $S_L$  is shorter than the hidden dimension (i.e.,  $S_L \ll d$ ), while long sequences significantly exceed it  $(S_L \gg d)$ . This distinction is crucial for understanding performance bottlenecks and it is summarized in Table 2.1 for the prefill phase.

**Table 2.1:** Impact of sequence length  $(S_L)$  relative to hidden dimension (d) on dominant operations and runtime scaling during the prefill phase [23].

| Case | Sequence Length Relative to $d$ | Runtime Behavior<br>and Dominant Layers            |

|------|---------------------------------|----------------------------------------------------|

| 1    | $S_L \ll d \text{ (Short)}$     | Linear layers dominate; scales $\mathcal{O}(S_L)$  |

| 2    | $S_L \approx d$                 | Mixed dominance; scales $\mathcal{O}(S_L + S_L^2)$ |

| 3    | $S_L \gg d \text{ (Long)}$      | Attention dominates; scales $\mathcal{O}(S_L^2)$   |

# 2.3 Speculative Decoding as a Token Generation Optimization Technique

Considering that the computational and memory demands of LLMs often exceed the capabilities of edge hardware, a number of optimizations are required to make LLM inference feasible in such environments. Key techniques can be categorized into three levels [27]:

- Algorithm-level optimizations: Quantization, pruning, distillation, sparse or conditional computation reduce compute and memory footprint.

- Hardware-level optimizations: Some techniques include: designing or leveraging specialized accelerators (e.g., NPUs), optimizing memory bandwidth, cache hierarchies awareness, exploiting parallelism, mixed precision arithmetic, and using near-memory computing.

- Software and system-level optimizations: Efficient operator kernels, LLM-oriented scheduling, memory layout optimizations, batching strategies, pipelining, runtime adaptation of models (e.g., dynamically choosing kernels depending on the request).

Although all these techniques are suitable for DNNs in general, a persistent bottleneck remains in the token generation process in the autoregressive decoding of LLM inference. Each token depends on previous tokens, leading to largely serial execution which limits latency improvements. This is where speculative decoding emerges as a promising technique at the algorithm-level to mitigate the sequential dependency.

### 2.3.1 Speculative Decoding Overview

Broadly, speculative decoding works by having a faster, usually smaller, drafter or speculator mechanism which predicts one or more future tokens (drafts), under the assumption that many of these predictions will be obvious or correct. Then a slower, more precise target model, also called verifier, checks in parallel whether those drafted tokens are acceptable according to some criterion. The target model receives that name since it is the model that would be used in a non-speculative setting and is aimed to be accelerated [28].

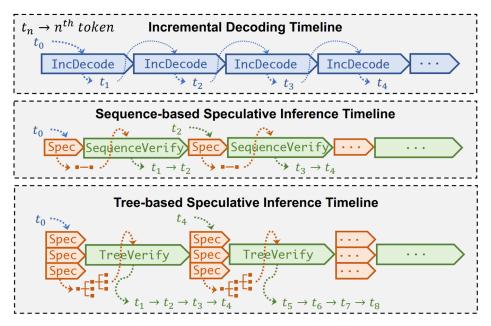

Figure 2.4 exemplifies the speculative decoding pipeline. At the top, the Incremental Decoding Timeline depicts the standard sequential execution of the decode phase without speculative techniques. The middle and bottom timelines present two speculative decoding strategies: sequential drafting and tree-based drafting. In both cases, the orange segments represent the speculative generation performed by a lightweight model, while the green blocks denote the validation phase carried out by the target model, which confirms or rejects the drafted tokens.

Key design dimensions for selecting an appropriate drafting mechanism include:

- **Drafting method**: Different techniques can be used as a computational-light way to generate tokens and in that way to assist on the token generation. For example, smaller independent models can be used [4], or models that share features from the target model [5]. Additionally, look-up tables and N-grams can be used since they excel in some generative tasks as summarization [28].

- **Draft length** ( $\gamma$ ): How many tokens ahead to predict. Larger  $\gamma$  offers more potential acceleration gains but risks more mismatches (thus, wasting computation). This is represented by the small orange squares bellow each drafting phase in Figure 2.4, where the value of  $\gamma$  is two for the sequence-based speculative decoding.

- Training and alignment of the drafting method: Draft models may be trained (or adapted) to better align with target model behavior (i.e., to match the target's output distribution); some techniques use multi-layer feature fusion or training-time testing to improve draft accuracy.

- Shape of the draft: Some techniques generate trees of candidate sequences (beams), adjusting the draft width depending on how well the draft aligns with target's distribution [28]. Other methods generate a single sequence instead.

The evaluation phase verifies the draft's proposed tokens, ensures correctness, and handles mismatches. Its main aspects are:

- Acceptance criteria and fallback: Depending on the desired quality, acceptance of drafted tokens might require either an exact match or looser criteria (e.g., the draft's token falls within top-k of the target's prediction). If many mismatches occur, a fallback to regular autoregressive decoding can be configured. This is quantified using the acceptance rate  $(\alpha)$ , which is the average of the number of accepted drafted tokens divided into the draft length  $(\gamma)$ . Usually,  $\gamma$  is balanced against  $(\alpha)$  [4].

- Overlap and mapping: Some speculative decoding algorithms [29] overlap drafting and verification to reduce idle time of the validation and drafting phases. For example, CPUs may generate drafts while GPUs verify concurrently prior speculations [29]. In

contrast, the examples in the middle and in the bottom of Figure 2.4 represent sequential speculative decoding pipelines.

Figure 2.4: Three generative pipelines: standard sampling (top, in blue), and two variants of speculative decoding: sequential drafting (center) and tree-based drafting (bottom). In both speculative approaches, the drafting phase is highlighted in orange, while the target model responsible for validating the generated drafts is depicted in green. Adapted from [30].

With  $\alpha$  and  $\gamma$  defined, we can compute the expected number of tokens produced in a single generative step. This step consists of a drafting phase, which generates a draft sequence of length  $\gamma$ , followed by a validation phase. We assume that the number of produced tokens follows a capped geometric distribution, with a cap of  $\gamma + 1$  and a success probability of  $1 - \alpha$  [4]. Under these assumptions, the expected number of generated tokens per generation step is given by Equation 2.1.

$$E(\# \text{ generated tokens}) = \frac{1 - \alpha^{\gamma + 1}}{1 - \alpha}$$

(2.1)

### 2.3.2 Dependence on Hardware and Software Configurations

While in speculative decoding the drafting and evaluation phases are critical for achieving an acceleration, the actual speedup depends strongly on the workload, the task, and the hardware-software environment on which the speculative decoding is executed. For instance, factors like the available memory, the memory bandwidth, and cache sizes can be used statically during model design or compilation to select the sizes of the depth and the width of a tree-based draft [31]. In devices with limited memory, the verification phase may require storing intermediate states, activations, or drafts, which may not be feasible. To mitigate this, the drafting phase can be interrupted as soon as some condition is met [32].

A formalism modeling the hardware impact on the speculative decoding speedup is developed in [4]. It presents the speedup as a function of the acceptance rate's expected value  $(\alpha)$ , the draft length  $(\gamma)$ , and the cost coefficient (c) which is a parameter that depends on the

hardware and software configuration. c is calculated as the ratio of the duration of one draft decoding step to that of the target model's duration. The speedup S is given by Equation 2.2.

$$S(\alpha, \gamma, c) = \frac{1 - \alpha^{\gamma + 1}}{(1 - \alpha)(\gamma c + 1)}$$

(2.2)

Ideally, the cost of introducing speculative decoding should be negligible  $(c \to 0)$ , leading to a speedup that is only function of the quality of the draft (i.e., how much is the average acceptance rate of the speculated tokens  $\alpha$ ) and the draft length  $(\gamma)$ . However, in practice, c is non-negligible and can significantly affect the speedup. For instance, if the draft model is not sufficiently faster than the target model or if the acceptance rate  $\alpha$  is low, the speedup may be minimal or below one.

We may also note that the condition  $c < \alpha$  must hold to achieve any speedup at all. This guarantees that there is at least one value of  $\gamma$  that yields a speedup greater than 1. Furthermore, the optimal draft length  $\gamma^*$  that maximizes the speedup depends on both the hardware configuration and the quality of the drafting mechanism.

### 2.4 Machine Learning Compilers

The slowdown of Moore's Law and Dennard scaling pushed the development of DSAs and exposed the limitations of general-purpose processors in handling increasingly complex ML workloads. While frameworks and libraries such as TensorFlow [33], PyTorch [34], and ONNX [35] have facilitated model deployment, they often rely on vendor-specific implementations that tightly couple software to particular hardware platforms [36]. This fragmentation leads to significant engineering overhead when porting models across diverse devices. To mitigate this challenge, the emergence of ML compilers marks a paradigm shift toward more generalizable and scalable deployment solutions. These compilers accept models from various ML frameworks, abstract their representations, and enable systematic optimization and retargeting across heterogeneous hardware.

### 2.4.1 Domain-Specific Compilers

ML is a paradigmatic case of a domain-specific application that has encouraged the development of its own Domain-Specific Language (DSL), such as the one used in PyTorch and compiled through TorchDynamo [34]. DSLs capture the abstractions and computational structures required by a specific domain, enabling more efficient optimization and compilation strategies compared to general-purpose languages. The tight coupling between ML workloads and DSLs motivates the design of domain-specific compilers [37], since conventional compiler infrastructures often fail to capture the semantics and optimization opportunities inherent in ML programs. DSLs allow higher level abstractions, while domain-specific compilers bridge this expressiveness with the performance needs of the underlying hardware. Nevertheless, ML systems face challenges that are not trivial from a compilation perspective: the frameworks often rely on fragmented "glue code", opaque kernels, and highly specialized operators that hinder systematic optimization [38], [39], [40].

Several approaches seek to reduce these challenges. Outside the ML field, Julia's design emphasizes enabling users to define high-performance numerical operators that are not opaque: user-defined operations are first-class, and the compiler can introspect, optimize, and compose [41]. Similarly, the newest version of Torch moves toward transforming Python bytecode into graph Intermediate Representation (IR)s that can be optimized, fused, and lowered, reducing the burden of custom operator implementation [34].

# 2.4.2 Multi-Level Intermediate Representation Approach for Compiler Construction

Multi-Level Intermediate Representation (MLIR) provides an infrastructure for compiler construction by supporting different levels of abstraction in a unified and modular framework, thereby facilitating the design of domain-specific compilers [42]. This approach promotes explicit representation of operations (MLIR's fundamental units of computation that consume and produce typed values), which enhances opportunities for optimization techniques such as operator fusion. Furthermore, it enables the definition of new DSL dialects, which are modular groupings of operations, types, and attributes tailored to specific domains (e.g., linear algebra), representations (e.g., control flow), or hardware targets (e.g., custom hardware).

MLIR's extensible transformation framework allows compiler passes to manipulate operations generically using traits and interfaces, enabling optimizations while preserving correctness. Through a process called lowering, high-level abstractions can be progressively transformed into lower-level dialects, bridging the gap between expressive domain-specific semantics and efficient hardware execution. In the context of ML compilation, MLIR allows for a clear separation across the compilation stack ranging from high-level tensor semantics to mid-level structured loop representations (e.g., affine dialects), down to low-level hardware-specific streaming semantics which expresses asynchronicity, parallelism, and temporal behavior in a dataflow-oriented execution model. This stratified design significantly improves the portability and efficiency of model lowering across diverse hardware backends.

### 2.4.3 IREE as a Compiler for Machine Learning

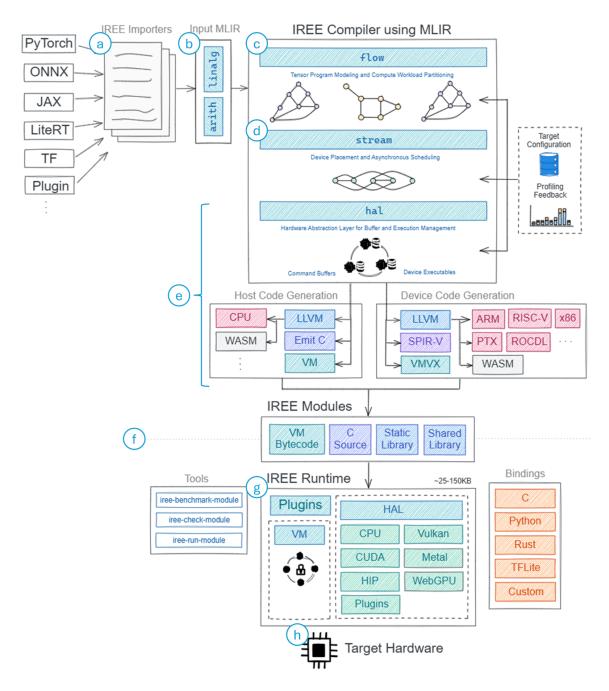

IREE [43] is a compiler and runtime project that builds directly on the concepts of MLIR, providing a concrete instantiation of multi-level compilation for ML workloads. The IREE ecosystem is presented in Figure 2.5. It ingests a program from a library or a DSLs (e.g., PyTorch backed by TorchDynamo) (Fig. 2.5 a.) through the importers. For PyTorch, the integration is handled by IREE Turbine, which exports models into the MLIR-based Torch dialect. ONNX models are first converted to MLIR using the iree-import-onnx tool, which produces the same Torch dialect. This design ensures that both PyTorch and ONNX models follow a common compilation path and reduces maintenance efforts. The compilation process in IREE initiates with three phases (Fig. 2.5 b.): the input phase, which lowers frontend dialects like Torch into core MLIR dialects such as linals; the ABI phase, which adapts the program's interface to the target execution environment (explained later) aided by IREE's util dialect; and the preprocessing phase, where tensor encodings are applied to enable data tiling and layout optimizations. This preprocessing enables hardware-specific transformations in later stages. Next, the global optimization phase performs high-level transformations such as

Figure 2.5: Ecosystem of Intermediate Representation Execution Environment (IREE) compiler and runtime highlighting its ML framework interoperability (top left) and its multitargeting capabilities (bottom). Modified from [43].

transpose propagation. Furthermore, it partitions the computation into dispatchable regions using integrating flow operations, preparing the module for efficient scheduling in further stages. The output at this point includes core MLIR dialects (linalg, arith, scf, tensor) and IREE's util dialect.

From now on, the program enters the middle-end phase and start diverging from tensor-semantics: first, the flow dialect (Fig. 2.5 c.) aims to the high-level dataflow and computation partitioning. It identifies dispatch regions and outlines them into executable units; this is a key for this thesis since it also allows the compiler to reason about which dispatch regions belong to which logical device, facilitating heterogeneity in downstream lowering. Next, the

stream (Fig. 2.5 d.) dialect intrudes a resource-centric, asynchronous execution model, and streaming semantics. Here, explicit lifetimes for resources are defined.

The stream and HAL dialects (Fig. 2.5 e.) adopt a unified abstraction for parallel execution that treats CPUs, GPUs, and other accelerators under a GPU-inspired scheduling model [43]. This design decision stems from the observation that ML workloads are inherently parallel and can benefit from the thread-workgroup-subgroup hierarchy familiar from GPU programming. The programming model adopted by IREE draws inspiration from Vulkan and OpenCL, offering mechanisms to partition workloads into parallel units, synchronize execution, and manage memory hierarchies. However, unlike Vulkan, where expert programmers must explicitly write low-level code, IREE automatically generates this code. This preserves high-level expressiveness for ML while still delivering fine-grained, device-specific performance. Between these two dialects (stream and HAL), IREE prepares for code generation through three phases: executable sources, executable configurations, and executable targets (Fig. 2.5 e.). In these stages, dispatches are translated and operations are materialized to target-specific dialects (e.g., LLVM (CPU), SPIR-V (Vulkan), PTX (CUDA)) demonstrating IREE's multitargeting capabilities; host-side code is lowered to vm dialect, which supports generic operations and enables portable execution. The final output is encapsulated in bytecode files, containing both host VM instructions and embedded device binaries (Fig. 2.5 f.).

### 2.4.4 Runtime for Heterogeneous Devices

While infrastructures such as IREE address many issues at the compilation stage, the runtime phase introduces additional challenges, particularly in the context of execution of ML workloads on heterogeneous and edge devices. The compilation phase alone cannot guarantee performance portability: runtime systems must also account for heterogeneity, communication costs, and dynamic workload behavior. This is especially relevant for edge and embedded devices, which are increasingly built on multi-core [44] and heterogeneous architectures, combining CPUs, GPUs, DSPs, NPUs and other specialized accelerators [39].

In this context, the role of the compiler is rethought in IREE. Here, the compiler is no longer seen as a purely offline tool. Instead, it interacts closely with the runtime to handle device-specific constraints and dynamic resource availability, without loosing modularity (Fig. 2.5 g.). Mechanisms such as IREE's Hardware Abstraction Layer (HAL) and the "Bring Your Own Codegen" principle in ML compilers [45] embody this approach by providing a modular interface where heterogeneous code generation and runtime execution can be reconciled, while abstracting away hardware-specific details (Fig. 2.5 h.).

Beyond heterogeneity, another key runtime challenge is the increasing dynamism in ML workloads. Many emerging ML models (e.g., those employing speculative decoding in LLMs) exhibit control flow that depends on data (e.g., early exits, recursion, conditional paths), varying input sizes, and dynamic architectures. This raises limitations for purely Ahead-of-Time (AOT) compilation, as well as for traditional Just-in-Time (JIT) techniques, particularly in resource-constrained embedded or edge environments. Using multiple precompiled kernels, and then using a scheduler to select them at runtime is an effort to address this and can balance the resource allocation accordingly [46].

# 3 Related Work

We can broadly define the related work under three main buckets: Firstly, other DNN optimization methods at the algorithmic level which tend to be orthogonal to our work. Secondly, the different methodologies that allow code generation and mapping of ML workloads onto many-core and heterogenous architectures to achieve high performance. The automatic techniques used in the deployment of such workloads on heterogeneous hardware constitute the third category. While each category addresses distinct challenges, they intersect in meaningful ways with the goals of this thesis.

### 3.1 Neural Network Optimization Methods

Deploying LLMs or even smaller neural networks on edge devices faces constraints in compute capacity, memory, energy, and thermal budget. Therefore, optimizing across multiple dimensions is essential to make inference feasible, efficient, and with acceptable latency and power consumption. Recent surveys categorize optimizations into three complementary classes: algorithmic methods, such as quantization, pruning, low-rank approximation, and knowledge distillation; hardware-specific optimizations, where accelerators like NPUs target both latency and energy efficiency [47], and mobile GPUs are exploited through tailored kernels [20]; and software techniques, such as ML compilers.

These approaches act orthogonally to the work of this thesis, enabling them to be combined, in principle; although, their effects are not always additive. For instance, while quantization reduces memory bandwidth demands and memory footprint, speculative decoding adds computational overhead (i.e., drafting and verification) which may offset, or reduce, the benefits coming from quantization. Therefore, a hierarchical framework is introduced in [48] to balance the trade-off between the drafting overhead and memory savings of quantization.

Additionally, some other works focus in the intersection of speculative decoding and hardware optimizations. Sequoia [31] adapts the generation of the draft tree to match hardware characteristics. DuoDecoding [49] explicitly schedules speculative decoding tasks across heterogeneous units to minimize the idle times. Similarly, Dovetail [50] splits speculative decoding work across CPU and GPU: some parts run on CPU, others on GPU. However, these

works do not consider heterogeneity on edge devices, focusing rather on high-end systems. In contrast, in this thesis we introduce heterogeneity on the level of a monolithic edge device.

### 3.2 Parallelism on Heterogenous Hardware

Mapping neural and non-neural workloads onto heterogeneous hardware has been a central theme in systems and accelerator research. The core challenge (how to partition computation and place work across devices with different instruction sets, memory hierarchies and peak throughput) has been addressed by a wide variety of methods, including polyhedral compilation, design-space exploration, combinatorial optimization, and runtime/adaptive scheduling. HeteroLLM [51] and Herald [52] extend these ideas to edge SoCs and to multi-DNN workloads, respectively. Tiramisu [53] and ZigZag [54] focus on space-exploration approaches for generating high performance parallel code using constrained optimization, analytical, or automatic approaches [55]. We build on these ideas, but focus on the unique challenges of speculative decoding, which introduces new dependencies and trade-offs not present in standard DNN inference.

Moreover, a challenge arises from the fact that heterogeneous platforms often integrate high-throughput accelerators (e.g., GPUs, NPUs) with general-purpose CPUs: severe load imbalance emerges when naive partitioning strategies are applied, since there is large disparity in the performance between these PUs. FlexInfer [56] explicitly characterizes this problem in the context of LLM inference and mitigates it by dynamically selecting the best mapping for each execution phase using both static hardware configuration and live runtime measurements. We translate these ideas into the context of edge devices, where AOT compilation is preferred over runtime scheduling due to the limited resources.

Additionally, multi-tenancy (i.e., placing multiple, concurrently active DNNs onto a shared heterogeneous platform) has been a study topic. MAGMA [57] formulates multi DNN mapping as an optimization problem and applies a genetic algorithm to identify near-optimal allocations of models to accelerator cores. Similarly, Adyna [46] addresses the scheduling of multiple dynamic DNN in spatial accelerators by formulating adaptive scheduling policies of different granularity. Both works highlight that multi-tenancy requires global reasoning about contention (compute and memory), model heterogeneity, and temporal interference, being pivotal to this thesis as well, where the the execution of the draft and the target model can be seen as a multi-tenant scenario. Nevertheless, MAGMA and Adyna evaluate against accelerator models or simulators rather than on silicon, as done in this work.

### 3.3 Machine Learning Compilers

Modern ML compilers exhibit different design decisions that influence their suitability for heterogeneous edge SoCs and speculative-decoding workloads. ONNX, primarily designed as an interchange format for ML models, prioritizes portability and operator coverage over compiler-oriented transformations. Its interpreter-style execution limits visibility of the full computation graph, hindering optimizations such as operator fusion, and its specification remains more aligned with ML representation than code generation needs. ExecuTorch [58] in

contrast, adopts a layered compilation architecture progressively lowering PyTorch models through structured abstractions while performing ahead-of-time memory planning.

Glow, one of the earliest end-to-end ML compilers, pioneered a two-phase intermediate representation (domain-level and low-level IRs) that enables aggressive graph lowering, static memory allocation, and backend-agnostic optimization [59]. However, its active development declined following the adoption of MLIR-based infrastructures that generalized its concepts. Finally, another early approach was TVM [60]. Influenced by Halide [61], TVM separates algorithm definition from scheduling, allowing autotuning and multi-target optimization across CPUs, GPUs, and accelerators.

Collectively, these systems illustrate the evolution from interpreted ML-specific runtimes toward progressively lowered, compiler-oriented stacks. While Executorch is a modern ML compiler system that adopts the modular multi-IR approach, it excludes high-level ML frameworks such as TensorFlow and ONNX. In contrast, our work build upon IREE, which supports interoperability across different high level ML frontends within a single IR [42]. This interoperability is crucial for enabling seamless integration of diverse models and workflows especially in heterogeneous environments where different tools rely on different ML ecosystems.

### 3.4 Thesis Contributions

This thesis distinguishes itself by being the first to power speculative decoding on edge devices through heterogeneous partitioning, a capability not addressed by prior works which either focus on high-end systems or lack multitarget deployment. Unlike existing approaches that rely on simulators, restrict themselves to homogeneous platforms or to commodity hardware, our method is evaluated on real silicon and leverages edge heterogeneity. This is allowed by the use a modern ML compiler and execution infrastructure: IREE, that uniquely supports multi-target code generation and interoperability across diverse ML frontends within a unified and layered intermediate representation, which is critical in edge scenarios where software stacks are fragmented and hardware diversity is high. Moreover, IREE's AOT compilation, backend-agnostic design, and extensibility make it particularly well-suited for existing and emerging edge devices, enabling the efficient deployment of speculative decoding on heterogenous platforms without vendor lock-in frameworks. To better contextualize this thesis' contributions, the Table 3.1 provides a comparative overview of representative works across these three dimensions, highlighting how our approach complements and extends existing efforts.

**Table 3.1:** Comparison of related works across key dimensions relevant to this thesis. reflects two important aspects: first, the deployment is not restricted to a single hardware vendor, ensuring broader applicability; and second, the evaluation is conducted on actual hardware platforms rather than relying solely on simulations or theoretical models. Spec. dec. stands for speculative decoding; quant., for quantization; het. for heterogenous; hier., for hierarchical.

| Work              | Spec. Dec.<br>on Edge | QuantAware<br>Spec. Dec. | Het. Partitioning | Based on<br>ML Compiler |

|-------------------|-----------------------|--------------------------|-------------------|-------------------------|

| Hier. Quant. [48] | ✓                     | ✓                        | ×                 | Х                       |

| Sequoia [31]      | X                     | ×                        | ×                 | X                       |

| DuoDecoding [49]  | X                     | ×                        | ✓                 | X                       |

| Dovetail [50]     | X                     | ×                        | ✓                 | X                       |

| HeteroLLM [51]    | X                     | ×                        | ✓                 | ✓                       |

| Herald [52]       | X                     | ×                        | ✓                 | ✓                       |

| Tiramisu [53]     | X                     | ×                        | ×                 | X                       |

| ZigZag [54]       | X                     | ×                        | ✓                 | ✓                       |

| FlexInfer [56]    | X                     | ×                        | ✓                 | ✓                       |

| MAGMA [57]        | X                     | ×                        | ✓                 | X                       |

| Adyna [46]        | X                     | ×                        | ✓                 | X                       |

| This Thesis       | ✓                     | <b>✓</b>                 | ✓                 | ✓                       |

# 4 Methods and Implementation

This chapter outlines the methodology and implementation for integrating speculative decoding into ML compilation workflows. It begins by detailing how abstractions can be aligned with hardware-aware execution to preserve productivity while enabling a good performance. The second section presents a systematic approach to distribute LLMs across heterogeneous and unbalanced PUs, formulating the problem as a design space exploration and optimization task. Together, these sections provide a foundation for deploying efficient, generative pipelines on edge systems.

### 4.1 Expressing Speculative Decoding Pipelines Ahead of Time

The problem formulated in this section has two interrelated facets: 1) performance: the integration of an autoregressive generative pipeline with speculative decoding into a compilation flow without sacrificing performance with respect to a baseline implementation, and 2) productivity: introduce a generative pipeline with speculative decoding at the right level of abstraction, one that maximizes ease of interaction and of definition/expressiveness. The interplay of these two aspects reflects the longstanding trade-off between performance and productivity. In the context of heterogeneous partitioning, this balance becomes delicate: the more abstract and flexible the system, the greater the potential for performance overheads. The key question, therefore, is how much performance degradation can be tolerated in exchange for the benefits of modularity, composability, and productivity.

# 4.1.1 Matching Abstractions of Speculative Decoding and Heterogenous Execution

Selecting an appropriate abstraction level for declaring the spatial partitioning turns into an ambivalence. On one hand, speculative decoding techniques are more naturally and clearly articulated in the higher abstraction layers, such as within ML libraries or DSLs. On the other hand, heterogeneous partitioning operates inherently closer to hardware, where fine-grained control over the computational and communication resources is essential. To reconcile this tension, we propose to rise the heterogeneous partitioning to the compiler's frontend,

integrating it directly with the speculative decoding construct. This decision is informed by observations in the literature (see Chapter 2) indicating that the ratio between the latencies of the speculative phase and the evaluation phase has a direct impact on the performance of speculative decoding techniques. Concretely, when the speculation phase execution time is not negligible, it becomes a bottleneck, making it a compelling optimization target.

By expressing the hardware-aware partitioning at the same level of abstraction of the speculative decoding logic, we preserve the flexibility and productivity gains of PyTorch level programming, while enabling targeted acceleration strategies. For instance, mapping the performance-critical speculative phase to an accelerated PU. This coarse-grained partitioning/scheduling approach is performed at the boundaries of the speculative phase and the evaluation phase, that is, spatially separating the large model from the small. Although a coarse-grained partition is also possible at the middle-end level of the ML compiler (e.g., flow and stream dialects in IREE), its benefits are diminished given increased complications: at this level, the interface between the speculative and evaluation phases are less obvious, necessitating a pattern matching mechanism to distinguish the two phases at the operation level. Such mechanisms are difficult to generalize to different model architectures or quantized variants, undermining scalability.

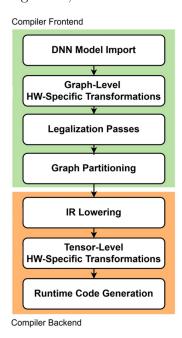

In contrast, the implementation of fine-granularity partitioning is more naturally implemented at deeper stages of the ML compilation pipeline [62], [63], [64]. This level of abstraction is better-suited for other type of optimizations such as the offloading of computationally intensive operations to specialized fixed-function accelerator units, including Multiply-Accumulate (MAC) arrays. Figure 4.1 shows the structure of a compiler framework that follows this principle: at the top level, the frontend performs graph-level transformations, while the backend focuses on finer-grained, tensor-level transformations.

Figure 4.1: An example of a compiler framework demonstrating partitioning at different granularities: graph-level in the frontend and tensor-level in the backend. Adapted from [64].

The coarse-grained partitioning we propose in no way precludes the possibility of a fine-granularity partitioning. For example, one could assign the token generation phase (also referred to as speculative phase) to a general-purpose PU A, and the second phase assigned

to another general-purpose processor, device B. Furthermore, data-intensive operations could be offloaded from both devices, A and B, to an accelerator C. However, communication costs increase and the advantage of offloading heavy operations to an accelerated unit must be considered more carefully to avoid degraded performance.

Inversely, the performance impact due to communications using a coarse-grained is smaller. The number of data exchanges between PUs is lower and it also requires less bandwidth. For example, in a autoregressive pipeline, where the token generation phase is mapped to a different PU than the evaluation phase, only two communication events are necessary per generation step: from the evaluation of the previous generative step to the current sequence generation phase, and from this to the next evaluation. Whereas a finer granularity requires several information exchange and synchronization events between the PUs in a single forward pass, significantly increasing the communication complexity. This overhead can become prohibitive if factors such as the number of memory banks, memory hierarchy, and relative speeds between memories and PUs are not carefully accounted for.

### 4.1.2 Implementation of a Monolithic Graph for Edge Deployment

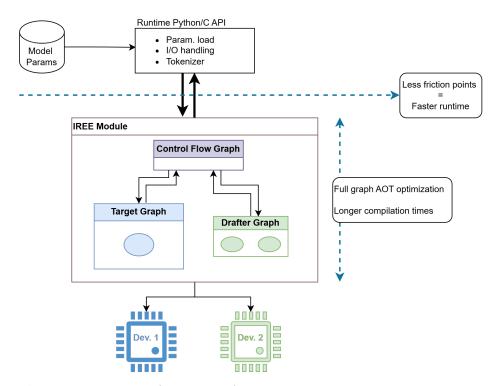

Figure 4.2: A single compiled graph (IREE module) contains the subgraph of the target model, of the drafter model, and the control flow graph that controls the generative pipeline interacting with the other two subgraphs. Within the same compiled IREE module, the device affiances are defined allowing an heterogenous execution.

IREE's capability (backed by MLIR) to integrate multiple dialect operations in a single program enables us to blend abstractions from different domains. This makes it possible to lift streaming semantics (like device affinities), together to high level tensor semantics. By lifting these semantics, an edge ML practitioner can manually (or even automatically) encode spatial partitioning without needing to manage device-specific details. This abstraction simplifies the design and improves portability between edge systems. In practice, IREE facilitates the injection of custom operators at the Torch graph level, making it possible to introduce low-level

constructs (e.g., device-level data-flow) into higher-level representations. This enables spatial partitioning to be expressed directly at the Torch module level. Operating at this level of abstraction, obviates the necessity of specifying the physical source and destination devices. Instead, it suffices to define monikers representing logical devices. These monikers are resolved to actual physical devices during compilation, allowing monikers to be mapped either to a single physical device or distributed across multiple devices, depending on the execution context and optimization strategy.

It is also worth noting that the procedural logic of speculative decoding (i.e., the algorithmic flow between drafting and verification phases, the acceptance logic, and the generative loop) is implemented within the same graph that contains the model arithmetic, as illustrated in Figure 4.2. The model's arithmetic components are depicted in blue and green, while the procedural logic is shown in grey; all encapsulated within the same IREE module. This monolithic representation of the entire generative pipeline has several advantages in the context of edge devices. For example, it is possible to perform end-to-end optimization across the entire pipeline. Similarly, this approach also minimizes the need of intermediary "glue code", which often introduces rigid boundaries between software modules and impedes global optimization. Furthermore, modularity is maintained, since each subcomponent of the pipeline can be encapsulated in a distinct subgraph, allowing independent replacement or refinement. For example, the speculation method could be changed in a modular manner without affecting the surrounding system. Moreover, deployment to hardware targets is streamlined, as the entire pipeline is represented as a single, self-contained artifact with minimal external dependencies, simplifying integration and reducing complexity. At the top of the same Figure, a minimalistic serving mechanism based on IREE runtime is depicted. It is responsible for loading the model parameters, handling user requests, generating responses, performing tokenization, and executing the IREE module

However, implementing the entire pipeline in an AOT and monolithic manner introduces notable challenges. Firstly, an increase in implementation complexity is expected, since partial rewrites of the code are required to ensure compatibility with graph capture mechanisms such as tracing. This issue is particularly critical for procedural logic involving control flow depending on dynamic data, where the number of possible execution paths can grow combinatorially. Such variability inflates the size of the computational graph and, in turn, increases the time required for global optimization and compilation.

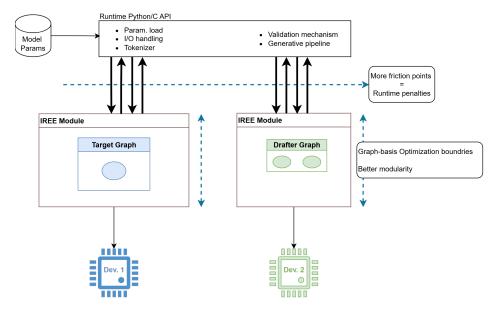

This limitation can be mitigated by transitioning from the monolithic approach shown in Figure 4.2 to a more modular design, as illustrated in Figure 4.3. In this setup, the previously monolithic module is split into two separate components, each containing only the model arithmetic for the target and drafter models. This enhances modularity, as changes performed to, for example, the drafting mechanism would require recompiling only the corresponding module rather than the entire previously presented monolithic graph, resulting in faster recompilation times. Additionally, compilation time is further accelerated because the procedural logic is not compiled into the modules but is instead implemented within the serving mechanism, which operates on top of the IREE runtime, as shown at the top of the figure. However, as previously noted, this introduces a rigid separation between the model arithmetic and the procedural logic, evidenced by the increased number of thick black arrows connecting the serving mechanism (top) to the IREE modules (bottom). On the positive side,

**Figure 4.3:** Each compiled graph (IREE module) contains only the model arithmetic and is assigned to a separate device. The control flow graph that orchestrates the generative pipeline is implemented within the serving platform, which is build on top of IREE runtime.

heterogeneous execution is simplified, as it is now distributed across two distinct compiled IREE modules.

## 4.2 Distributing Large Language Models across Unbalanced Processing Units

Another challenge we address is the mapping of a computational graph representing an LLM with speculative sampling and the assignment of its subgraphs to different PUs within a heterogenous system, specifically on an SoC. We focus on the prefill phase and short sequence lengths  $(S_L)$  of the generative pipeline. This is formulated as an optimization problem, for which we define the search space encoding, the search strategy, and the evaluation methodology.

Although the focus of the work is on the prefill phase, the method can be extended to other execution regimes such as the decode phase and to large sequence lengths. The prefill phase, which is the dominant contributor in Time to First Token (TTFT), is a critical determinant of responsiveness in real-time and edge deployments of LLMs. TTFT optimization directly impacts not only user-perceived latency but also total system performance [65]. This is especially important in applications like online translation, where low TTFT ensures fluid and near-instant feedback.

#### 4.2.1 Evaluation Hardware

The NXP i.MX95 SoC is used as a hardware platform to evaluate the method presented in this section. This SoC is an example of an edge-targeted applications processor integrating multiple compute engines designed for general compute, graphics, and neural acceleration [19]. This heterogeneous device contains six ARM Cortex-A55 cores to handle generic applications, control logic and orchestration of tasks; a single-shader-core Mali-G310 GPU intended for

graphics processing but also usable for data-parallel compute and ML workloads. Therefore, our focus is on the CPU and GPU components of this SoC, which allow the execution of entire LLM architectures. These two devices are described in more detail below:

- Hexacore Cortex-A55 CPU: This is an energy-efficient general-purpose PU. The Cortex-A55 supports typical ARMv8 features (e.g., 64-bit addressing, NEON SIMD, and intersupport) [66]. Given its limited memory bandwidth and lower compute density, using the CPU for full transformer attention layers or large matrix multiplies is often inefficient.

- Mali-G310 GPU: This is a single-shader low-power mobile GPU supporting efficient execution of vector and tensor operations and recent graphics APIs such as OpenCL and Vulkan. The GPU offers shader pipelines and parallelism for tasks amenable to Single Instruction Multiple Threads (SIMT) execution (e.g. matrix multiplications, elementwise activations) [67].

### 4.2.2 Assumptions

To constraint the search space, we assume that the parameter  $\alpha$  (the expected value of the acceptance rate, see Equation 4.1) is known prior to compilation. This value is determined by the specific combination of drafting and evaluation methods employed and algorithm-level optimizations and can be assessed from an evaluation of the speculative decoding method on particular datasets and tasks. Regarding the hardware side, we assume that the system configuration (i.e., PUs and their availability) is also known a priori: for multiple PUs (cores on a CPU, shader units on a GPU, or processing elements in an NPU), we assume that the number of available cores for inference  $n_p$  of each PU P remains constant during runtime. Consequently, we do not consider scenarios involving dynamic resource contention from other processes, which would cause a dynamic variability in the available computational resources. In other words, we restrict our analysis to cases where information is available AOT to enable spatial partition of the workload on the highest-performing combination of PUs. Therefore, the input for our optimization problem requires: the acceptance rate  $\alpha$  (corresponding to the speculative decoding algorithm) and the system configuration (i.e., a list of available PUs with their possible configurations and the number of available cores).

Additionally, we restrict scheduling of the computational graph to spatial partitioning only, excluding any form of temporal scheduling. This simplification reduces the complexity of the search space, although it comes at the cost of flexibility. In practice, the computational load during LLM inference varies, for example, between the prefill and decoding phases, or as the KV cache grows from small to large. Dynamically reassigning subgraphs to different PUs during runtime could yield performance benefits, but such dynamic scheduling is beyond the scope of this work. Instead, we consider only the initial phase of inference, where the KV cache size is either empty or small, and the sequence length is much shorter than the model's hidden dimension. In this regime most of the computations are concentrated in the projections layers of the Feedforward Neural Network (FNN) section.

Finally, we assume that the speculative decoding strategy proceeds sequentially, with the lightweight drafting phase followed by the evaluation phase. Speculative decoding algorithms

that overlap these two phases, such as pipelined or interleaved approaches, are considered out of scope for this study.

### 4.2.3 Design Space Encoding

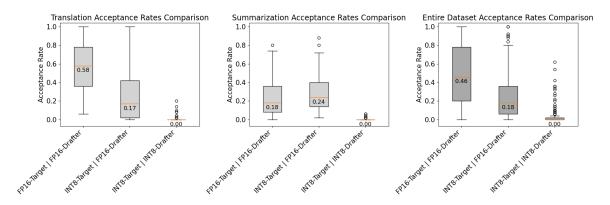

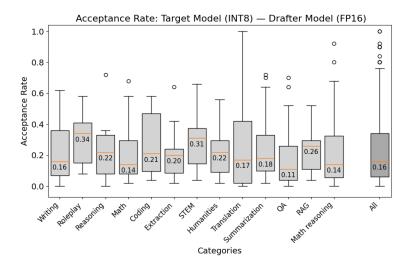

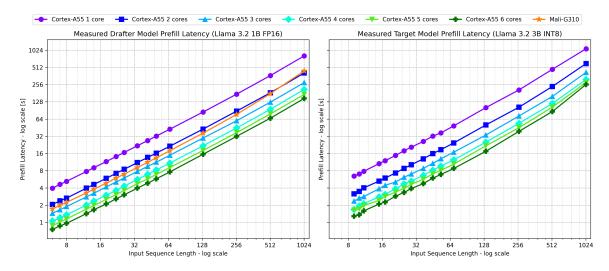

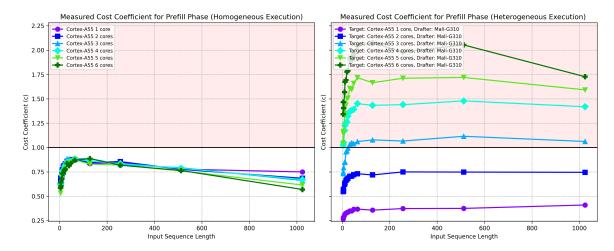

The search space we consider consists of the combinatorial set of valid assignments of subgraphs from the computational graph to PUs that support all operations within each subgraph. Each PU is characterized by a specific configuration, namely, a specific number of cores available for the inference task. This is a case of combinatorial distribution that includes m subgraphs that can be assigned to n processors, where 1 < n < N, and N is the total number of available processors in the set  $\{n_1, n_2, ..., n_N\}$ . Each subgraph must be assigned to one processor, but there may be processors without any assigned subgraphs. The number of available combinations will be:  $N^m$ .